## FONDEMENT DES SYSTÈMES NUMERIQUES

SPACES: Security evaluations of Physically

Attacked Cryptoprocessors in

Embedded System

Program: ANR/JST-2010

## PROJECT OBJECTIVES

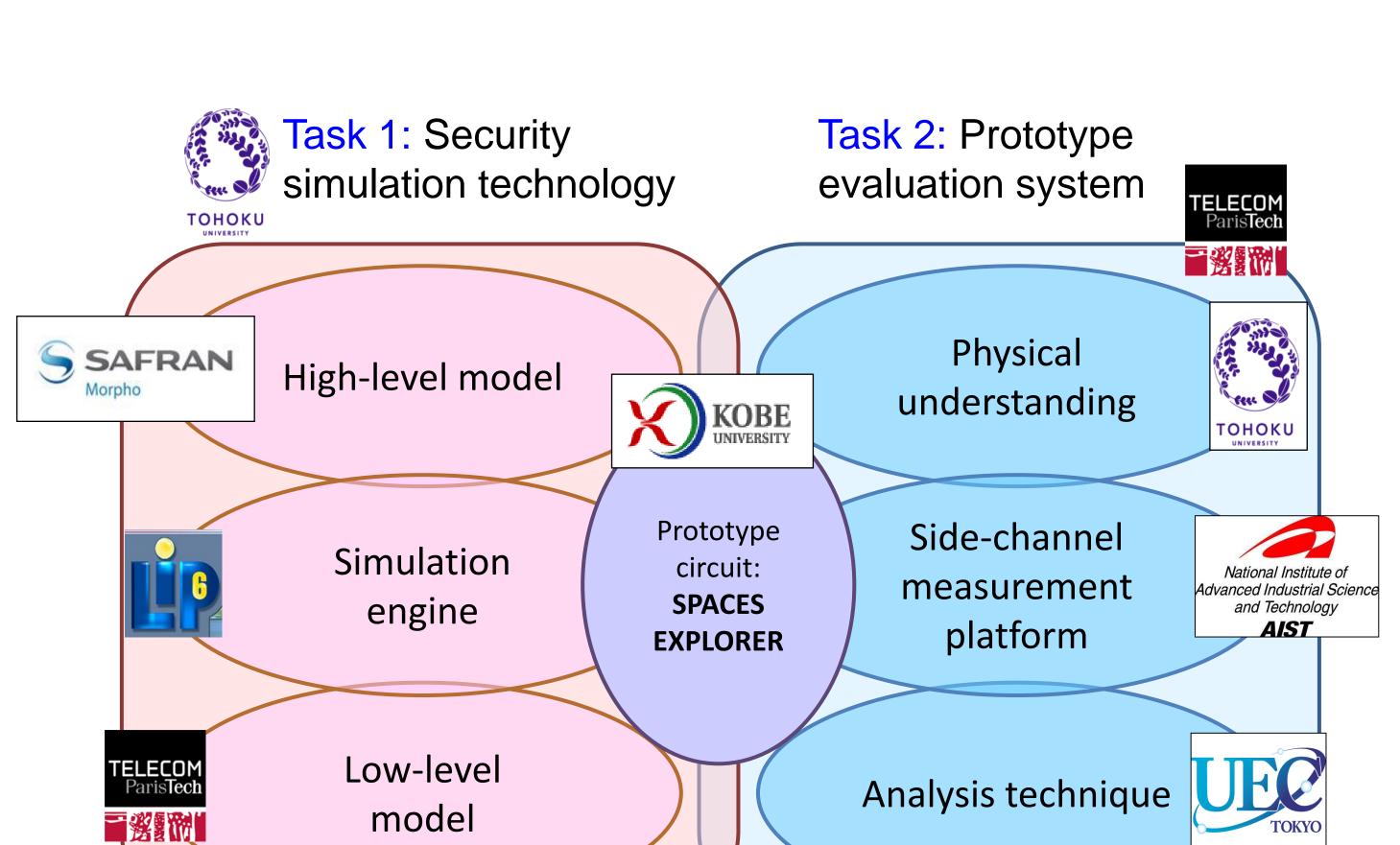

Aims to establish a novel security-evaluation methodology to assess crypto-modules in embedded systems, precisely:

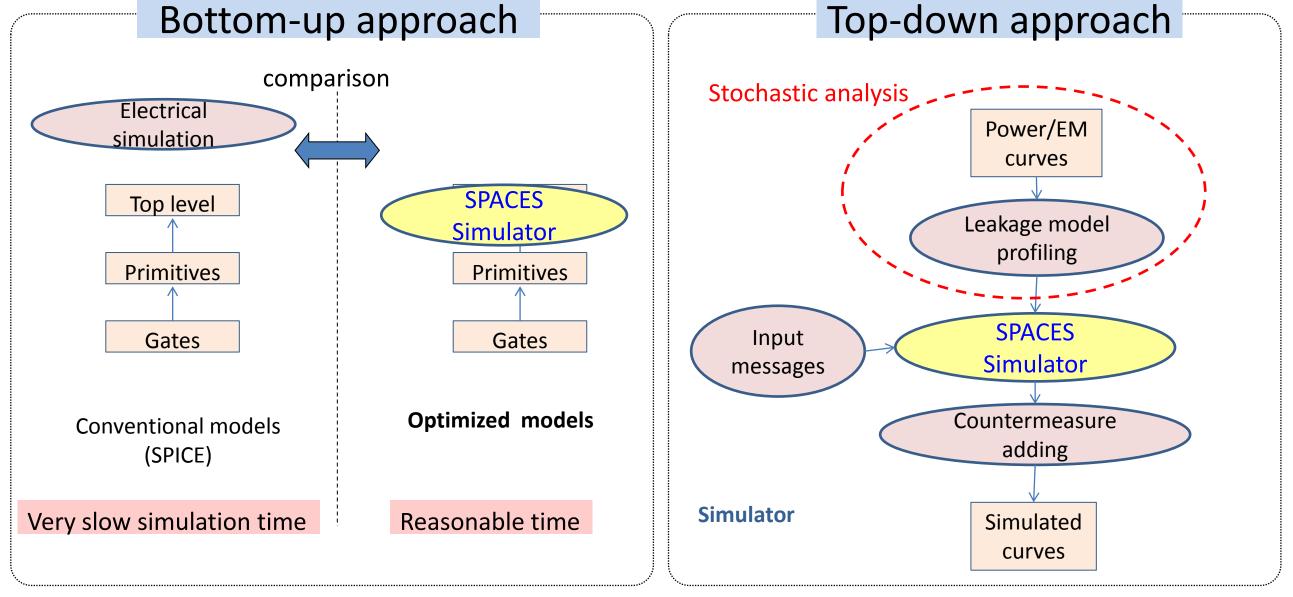

- 1. Study and develop a trustworthy **SPACES Simulator** for evaluating crypto-circuits against side-channel attacks before their fabrication.

- 2. Develop **evaluation platforms** for validation: FPGA/smartcard platform + ASIC prototype chip.

- 3. Study of new attacks for a better understanding of leakages and faults, in particular by the ElectroMagnetic channel.

Fig 1: Project structure

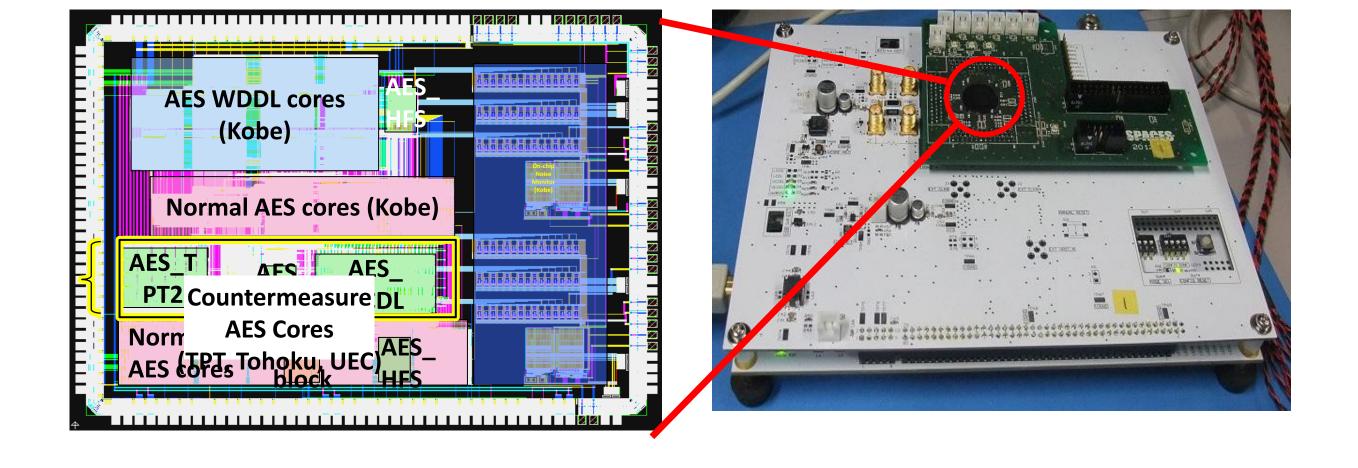

Fig 2: SPACES Explorer mounted on SASEBO-W

Fig 3: Simulation approaches

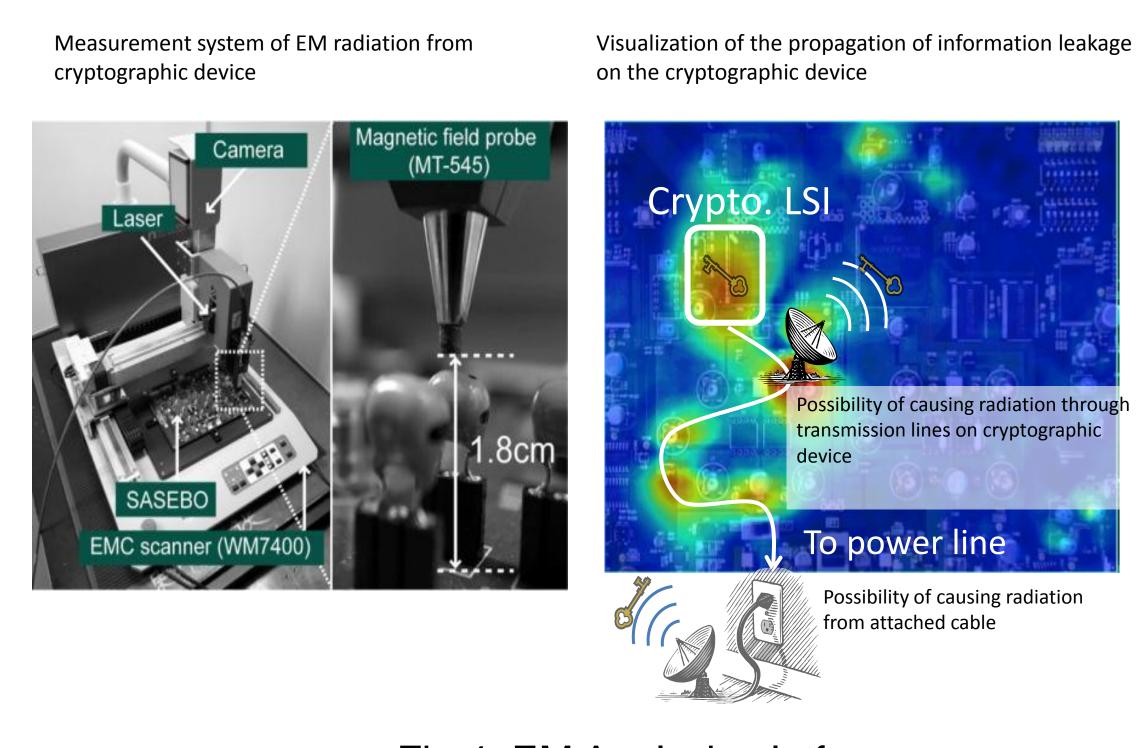

Fig 4: EM Analysis platform

The following results have been obtained:

- 1. A prototype chip "SPACES Explorer" successfully taped-out and tested with 20 crypto-cores in TSMC 65nm technology

- 2. A new FPGA board **SASEBO-W** for smartcard and prototypes evaluation against side-channel attacks

- 3. A functional **High-speed Simulator** for side-channel assessment

- 4. An **EM analysis platform** for both side-channel and fault attack understanding

- 5. A new attack type study: Fault Sensitivity Analysis

## CONCLUSIONS AND PERSPECTIVES

- Very close collaboration between french/japonese partners

- Many results: prototypes, software tools, new attacks, international publications(>20)

- SPACES explorer functionally tested, under security evaluation

- Perspectives to continue with the same team in another framework

COORDINATORs: Télécom Paristech, Tohuku University

JST PARTNERS: Tohoku University, Kobe University, UEC, AIST

ANR PARTNERS: Télécom Paristech, Paris 6 (LIP6), Safran Morpho

**AIST**